Yesterday I had the great pleasure to talk over at FOSSCOMM 2024 about CISC vs RISC, a historical analysis, why RISC should be worked on due to energy efficiency concerns, HPC applications of RISC processors, and the future of open source ISAs like RISC-V and possible extensions focusing on HPC related workloads like matric multiplications.

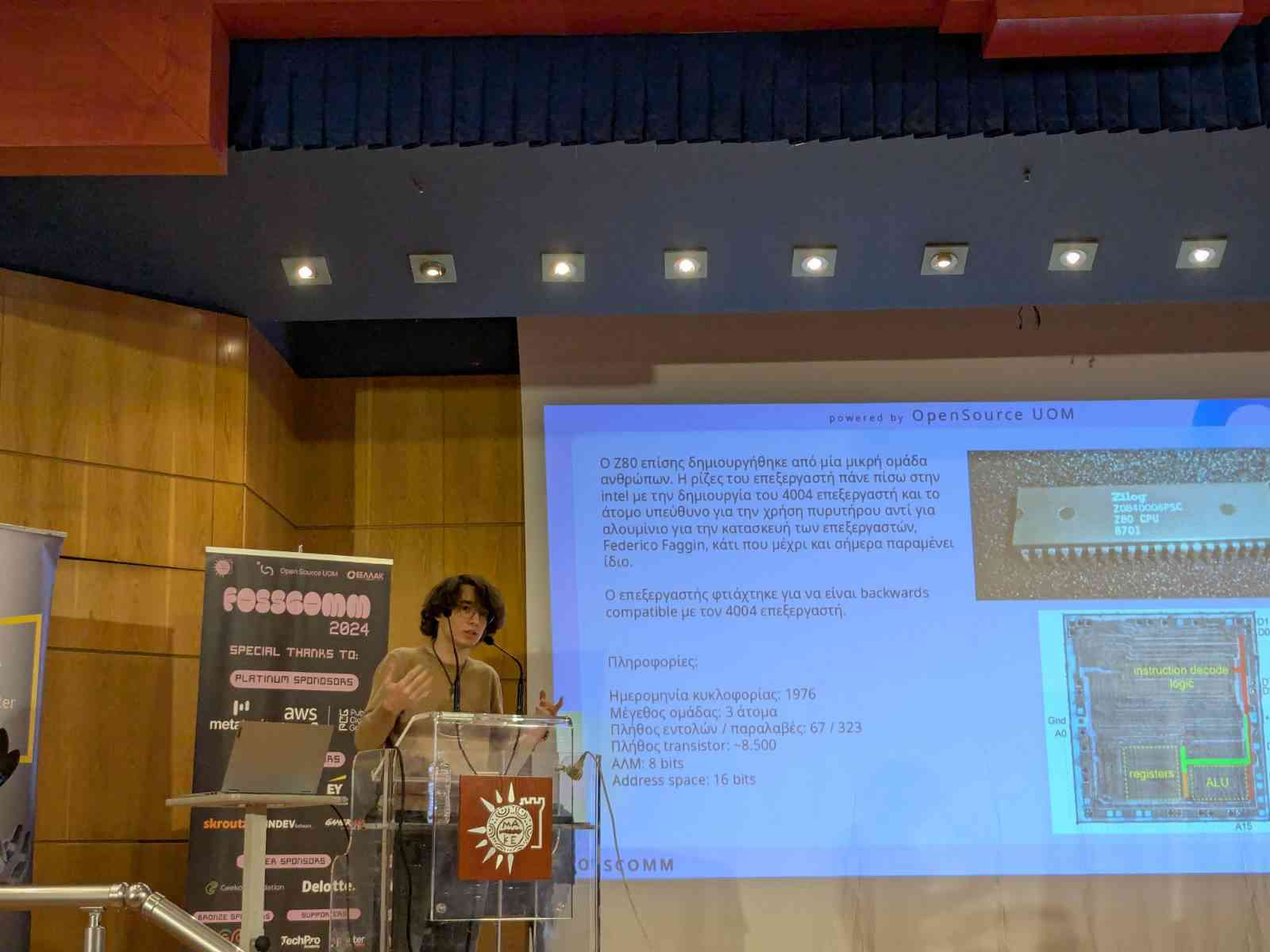

Yes, that is me, and yes I did talk about the Z80, I actually talked about the following CPUs:

- 6502

- Z80

- 8086

- ARM1

- Motorola 68020

I also talked about how decoders in CISC design use from 4% all the way to 10% of a CPUs power consumption and how this is only worsened by the backwards compatibility provided by the x86 ISA as well as the microcode since it does introduce some amount of overhead.

I should say this before I close things up, I am not, by any means, against microcode, it was designed and implemented when it should have been and it is a wonderful technology that opened the gates for more easily modifiable processors, but that came at a cost. Since microcode basically emulates certain instructions it, as a result, consumes more power. I won't dive into the topic of execution speed since I am not qualified enough to talk about this now.

My next goal is to deepen even further my knowledge on CPU design and computer architecture as well as design my own custom made CPU with my own custom RISC ISA.